# **UNIVERSAL TRAINER**

# **REFERENCE MANUAL**

## COPYRIGHT EMAC INC. CARBONDALE, IL

May 10, 1993 REVISION 1.3

CONTROL

EQUIPMENT MONITOR AND

CARBONDALE, IL 62901 618-529-4525

## TABLE OF CONTENTS

| SOFTWARE FEATURES                                                                                                                                                                                                                   | 1                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| HARDWARE FEATURES                                                                                                                                                                                                                   | 1                                |

| SOFTWARE REFERENCE   KEYPAD DESCRIPTION   MOS SERVICES   TERMINATING PROGRAMS   USING INTERRUPTS                                                                                                                                    | 3<br>13<br>18                    |

| HARDWARE REFERENCE 2   EMAC TRAINER BOARD AND CIRCUIT DESCRIPTIONS 2   SERIAL COMMUNICATIONS 2   ANALOG INPUT 2   PARALLEL PRINTER PORT 2   TIMER / COUNTER AND SPEAKER 3   PARALLEL PERIPHERAL INTERFACE 3   JUMPER DESCRIPTIONS 3 | 21<br>24<br>26<br>27<br>30<br>31 |

| OPTIONAL ON BOARD HARDWARE FEATURES                                                                                                                                                                                                 | 36                               |

| OTHER OPTIONS FOR TRAINER SYSTEMS                                                                                                                                                                                                   | 36                               |

## APPENDICES

- A. UNIVERSAL TRAINER CONNECTORIZATION

- B. ASSEMBLY LANGUAGE LISTING OF THE MONITOR OPERATING SYSTEM

- **C.** SCHEMATICS

## SOFTWARE FEATURES

- \* Easy data entry via keypad and display or PC/dumb terminal.

- \* Ability to scan all 64K of memory space.

- \* Ability to change any RAM location.

- \* Ability to execute from any memory location.

- \* Ability to single step or run full speed with break.

- \* Examine and change the contents of any register.

- \* Separate user stack area.

- \* Ability to store user programs on board to RAMDISK or externally to PC.

- \* Ability to upload and download Intel hex files.

- \* Monitor Operating System provides services for I/O devices including LED display.

- \* I/O device Assembly Language drivers provided.

## HARDWARE FEATURES

- \* Timers, UARTs, digital I/O ports, A/D, D/A, and DIP switch are all user accessible I/O devices.

- \* 1 eight bit digital input port connected to an eight position dip switch with status LED's.

- \* 1 eight bit digital output port with status LED's.

- \* 4 channel eight bit ( ten bit optional ) analog to digital converter.

- \* Analog signal conditioning card slot for optional signal conditioning of analog inputs.

- \* 1 RS232 serial port and 1 RS485 network port.

- \* 3 sixteen bit timer counters with gated inputs.

- \* 12 hardware interrupt sources.

- \* 8 character, 14 segment alphanumeric LED display with 28 key keypad.

- \* Status LEDs for address, data, and system status lines.

- \* Hardware single step with hardware breakpoint.

- \* Easy access to analog and digital I/O through screw terminal connectors.

#### INTRODUCTION

The Universal Trainer (UT) is a full featured computer providing the user easy programmability, yet access to sophisticated I/O devices. The self-contained unit consists of a single circuit board with user manual and wall mounted power supply. The unit contains a Monitor Operating System in EPROM allowing the user to single step, run full speed with breakpoints, and easily access and modify the microprocessor registers. User programs can be written virtually anywhere within the RAM space, providing ample room for even complex programs. Programs can be retained even with loss of power with optional RAMDISKs. Assembly Language Subroutine Drivers and MOS Services are provided for each I/O device to ease programming.

EMAC offers several options for the Universal Trainer including: Blank analog signal conditioning cards as well as conditioning cards for temperature, pressure, voltage, current, and more. Additional digital I/O, real time clock, EPROM programmer, networking, and IBM PC support software are also available.

## SOFTWARE REFERENCE

The Monitor Operating System (MOS) is a powerful software program that provides the user with the tools to enter and edit programs as well as run, test, and debug machine language programs. When the Universal Trainer is first turned on, interaction between the Monitor Operating System and the user is through the onboard keypad and display. The Extended Monitor Operating System (EMOS) can be invoked from this mode to allow interaction through a dumb terminal/PC. Each mode of interaction has its advantages and disadvantages.

## Interaction Through Keypad and Display

When the Universal Trainer is first turned on or reset, all interaction with MOS is through the on-board keypad and display. This mode is highly functional for entering and debugging code. The major advantage of this mode is its ability to be used stand-alone (without any external hardware). This allows the UT a degree of portability not found in dedicated systems (those requiring a dumb terminal or PC). Another advantage of this input mode is cost. The unit can be purchased and used without having to purchase a dumb terminal or PC.

The keypad display mode uses eight, fourteen segment alphanumeric LEDs for display output. This type of display is similar to the displays used in calculators, but allows letters in addition to numbers. The ability to use letters gives the UT an advantage over other seven segment LED display based

trainers. The UT is able to give descriptive prompts to the user making it easier to use.

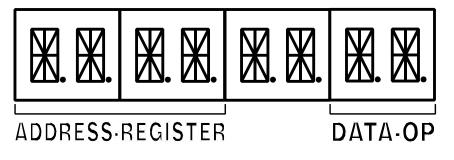

The display at power-up reset, contains the default PC address (8F01H) in the left four characters of the display. This is what is referred to as the ADDRESS/REGISTER FIELD. In the right two characters is the contents of the displayed address. This field is known as the DATA/OP FIELD (see diagram).

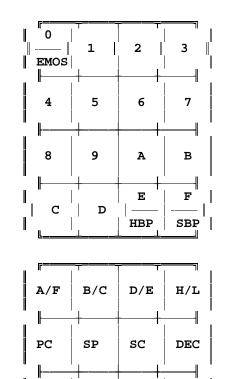

The keypad display mode uses a twenty-eight key keypad for input. Each key has tactile feel (clicks when pressed) and produces an audible tone when pressed providing feedback for the user. The MOS controlled keys are in two groups of sixteen and twelve. The group of sixteen are Hexadecimal numeric keys (0 - F). The group of twelve keys are command keys. These keys allow the user to examine registers, change their contents, single step, and a variety of other functions. One of the 12 command keys is a FUNC. key, similar to a SHIFT key, providing additional functions when used with the Hex numeric keys. The UT has an additional 8 keys that are not included in the two groups mentioned above. These keys control hardware functions and are described elsewhere.

#### The layout of the twenty-eight key keypad for the Universal Trainer is as follows:

FUNC

ENT

RUN

STP

#### KEY(S) DESCRIPTION

- **0-F** Numeric keys. When a numeric key (0-F HEX) is pressed, the numeric value appears at the right side of the data field display. To correct an entry error just repeat, using the correct number key and the error will be overwritten.

- A/F This key displays the contents of the A register (Accumulator) and the condition Flags. The A register and the flags are displayed as four HEX digits. The two digits on the right of the display represent the contents of the A register and the two on the left represent the condition Flags. The displayed value may be changed by entering the desired HEX number using the numeric keys and then pressing the ENT key. The condition Flags are defined bit by bit as follows:

| BIT 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CARRY FLAG                                               | (a set condition indicates a carry)                            |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------------|--|--|--|

| BIT 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | NOT USED                                                 |                                                                |  |  |  |

| BIT 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PARITY FLAG                                              | (a set condition indicates an even number of bits, odd parity) |  |  |  |

| BIT 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | NOT USED                                                 |                                                                |  |  |  |

| BIT 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | AUX. CARRY FLAG                                          | (a set condition indicates a carry from bit 3 to bit 4)        |  |  |  |

| BIT 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | NOT USED                                                 |                                                                |  |  |  |

| BIT 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ZERO FLAG                                                | (a set condition indicates a zero result)                      |  |  |  |

| BIT 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SIGN FLAG                                                | (a set condition indicates bit 7 of the A register is a 1)     |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ample if the display reads<br>dicates the A register con | s: 0044 A/F<br>Itains 0 and the ZERO and PARITY Flags are both |  |  |  |

| This key displays the contents of the B/C register pair. The B/C register pair is displayed as four HEX digits. The two digits on the right of the display represent the contents of the B register and the two on the left represent the contents of the C register. The displayed value may be changed by entering the desired HEX number using the numeric keys and then pressing the ENT key.                                                                                                          |                                                          |                                                                |  |  |  |

| This key displays the contents of the D/E register pair. The D/E register pair is displayed as four HEX digits. The two digits on the right of the display represent the contents of the D register and the two on the left represent the contents of the E register. The displayed value may be changed by entering the desired HEX number using the numeric keys and then pressing the ENT key.                                                                                                          |                                                          |                                                                |  |  |  |

| This key displays the contents of the H/L register pair. The H/L register pair is displayed as four HEX digits. The two digits on the right of the display represent the contents of the H register and the two on the left represent the contents of the L register. The displayed value may be changed by entering the desired HEX number using the numeric keys and then pressing the ENT key.                                                                                                          |                                                          |                                                                |  |  |  |

| This key displays the contents of the PROGRAM COUNTER. The PROGRAM COUNTER (PC) is a 16 bit register, displayed as four HEX digits. The displayed value may be changed by entering the desired HEX number using the numeric keys and then pressing the ENT key. The PC defaults to address 8F01 at power-up.                                                                                                                                                                                               |                                                          |                                                                |  |  |  |

| This key displays the contents of the STACK POINTER. The STACK POINTER (SP) is a 16 bit register, displayed as four HEX digits. The displayed value may be changed by entering the desired HEX number using the numeric keys and then pressing the ENT key. The SP defaults to address FFD4 at power-up.                                                                                                                                                                                                   |                                                          |                                                                |  |  |  |

| This displays the two bytes that are at the top of the stack, or in other words, the data that would be removed from the stack if a POP instruction were executed. The left two displays show the byte at SP + 1 (stack pointer address + 1) and the two displays to the right of this represent the byte at SP. The displayed value may be changed by entering the desired hex number using the numeric keys and then pressing the ENT key. The top of the stack (SC) is initialized to zero at power-up. |                                                          |                                                                |  |  |  |

B/C

D/E

H/L

PC

SP

SC

- **DEC** This key allows the user to decrement through memory, thus subtracting 1 from the PC every time the DEC key is pressed. The current PC address (4 HEX digits) and the contents of that address (2 HEX digits) are displayed. The address contents may be changed by entering the desired HEX number using the numeric keys and then pressing the ENT key.

- **STP** This key causes the microprocessor to execute one instruction (single step) at the current PC address. Single Stepping is a valuable debugging tool that allows the user to examine registers and memory after each instruction executes. The STP key invokes a software single stepper that executes one user instruction and then returns to Monitor Operating System ready to except another user command. Unlike the Hardware Single Stepper, the Software Single Stepper requires the processor be active throughout the single stepping process. If single stepping a Service Call, the processor will execute the Service Call at full speed and stop at the instruction immediately following the Service Call (see section on single stepping for additional information).

- **RUN** This key cause the microprocessor to execute a program at full speed starting at the current PC address. The program will continue to execute until an optional hardware or software breakpoint is encountered, a key is pressed, or until a RST 7 (0FFH) instruction is executed.

- **FUNC.** This key selects the second function of the keys that have two functions. When this key is pressed "FUNCTION" will appear on the displays and if a key is pressed which has a second function, that function will be performed.

- **ENT** When the UT is turned on or reset the MOS is in data entry mode. When in this mode, pressing ENT will cause the data which is shown on the right two displays to be stored into the address pointed to by the PC register (which is shown on the left four displays) and the PC register will be incremented. When registers or hard or soft breakpoints are being displayed, pressing the ENT key causes the data that is being displayed to be stored in that register or for that breakpoint to be set. If in any mode you have typed some numbers and you want to restore the original value, you can restore them if you haven't press ENT yet. Press the "Func." key twice and you will be back in data entry mode and the data, registers or breakpoints will retain their original values.

- (Below are the second functions of the dual function keys)

- **EMOS** This starts the EMOS (Extended Monitor Operating System). This requires that a PC or dumb terminal be connected to COM1.

- **HBP** This key displays the current Hardware Breakpoint address. The displayed value may be changed by entering the desired breakpoint address in HEX using the numeric keys and then pressing the ENT key. The act of pressing the ENT key is what arms the Hardware Breakpoint arming circuit. A hardware breakpoint can only occur when the circuit is armed. Upon the occurrence of a Breakpoint, the Hardware Breakpoint address is still maintained, however the Hardware Breakpoint arming circuit is disarmed. To rearm the hardware breakpoint for the same address simply press the HRD BRK key followed by the ENT key. NOTE: If the program execution never accesses the breakpoint address, the program can not stop at the breakpoint address. The hardware breakpoint, breaks at any address including those in EPROM and operand addresses (see Section on breakpoints for additional information).

- SBP This key displays the current Software Breakpoint address. If 0000 is displayed,

then no breakpoint has been established. The displayed value may be changed by entering the desired breakpoint address in HEX using the numeric keys and then pressing the ENT key. Upon the occurrence of a Breakpoint the Software Breakpoint address is automatically reset to 0000. NOTE: If the program execution never reaches the breakpoint address or the breakpoint address is not that of an opcode, the program will not stop at the breakpoint address. Also any address specified that references addresses in EPROM (addresses below 8000 HEX) will not stop execution, even if the opcode at that address is executed (see section on breakpoints for additional information).

#### Interaction Through a Dumb Terminal/PC

The most productive way to use the Universal Trainer is through EMOS in which all interaction is through a dumb terminal/PC. This mode obviously allows more information to be exchanged easier than with the keypad display mode. Additional functions are available through the dumb terminal/PC mode that are not possible with the keypad display input mode.

When a dumb terminal/PC is available you may connect it to the Universal Trainer and invoke EMOS by pressing "Func." then the "EMOS" key. The following will appear on the terminal display:

#### EMOS Vx.xx HELP MENU

B --> Bring Block from RAMDISK to Memory C --> Change register contents D --> Dump memory contents E --> Edit memory contents F --> Fill memory with byte G --> Go execute program { full speed } H --> Hex/Decimal math {1st + 2nd, 1st - 2nd} I --> Input from I/O port L --> List memory contents using mnemonics M --> Move section of memory 0 --> Output to I/O port P --> Printer ON/OFF R --> display Register contents S --> MOS Service call T --> Trace program execution W --> Write memory to RAMDISK block < --> hex download from trainer to host > --> hex upload to trainer from host ? --> display this help menu

The above Help Menu can be displayed at any time from the EMOS - prompt by typing a ?. Each of the EMOS commands are invoked by type a single character at the EMOS prompt. EMOS will prompt the user for any necessary command input and checks the input to be sure it is of the proper form. When an "ADDRESS" is requested, a number of up to 4 HEX digits should be entered. When a "BLOCK" is requested, a number of up to 3 DEC (decimal) digits should be entered. The "escape" key or bad input will abort the issued command and cause a "?" to be displayed. Following are descriptions of the EMOS commands.

#### EMOS COMMAND SUMMARY

"B" The Bring Block command allows the user to copy a block (256 bytes) or blocks of data from RAMDISK to memory.

When the Bring Block command is issued, the Monitor responds with:

#### DEST. ADDRESS ....

Enter the starting memory address, up to 4 HEX digits, where the RAMDISK data will be copied to.

The Monitor then responds with:

#### **STARTING BLOCK ...**

Enter the starting block number, up to 3 DEC digits, of the desired first block. **NOTE:** RAMDISK slot 1 contains blocks 1 - 128, and slot 2 contains blocks 129 - 255.

The Monitor then responds with:

#### NUMBER OF BLOCKS ...

Enter the number of blocks, up to 3 DEC digits, that are to be copied to memory.

**NOTE:** If (STARTING BLOCK + NUMBER OF BLOCKS) is greater than 255, the monitor will display:

#### ERROR BLOCK OUT OF RANGE !

and, after a short delay, return to the system prompt.

"C" The Change command allows the user to change any of the microprocessor's registers, the top element of the stack and the current memory location pointed to by the program counter.

When the Change command is issued, the Monitor program first displays the current contents of all the registers, and prompts the user with:

## SELECT REG. [F,A,B,C,D,E,H,L,T,S,P,O]..

The Monitor then expects one of the capital letters contained within the brackets to be entered. The letter "F" stands for the Processor Status Word Flags, "A" is the Accumulator and "B,C,D,E,H,L" are the 8085 General Purpose Registers of the same name. Each of these registers can contain at most 2 HEX digits (8 bits). The letter "T" stands for the "top of stack" which are the next two bytes to be removed from the stack. Though this is not an actual register, it is treated like one so you can view and/or change the value on the top of the stack. The letter "S" stands for the Stack Pointer, which is initialized at power-up to address FFD4 HEX. The letter "P" stands for the Program Counter, which is initialized at power-up to address 8F01 HEX. Each of these registers can contain at most 4 HEX digits (16 bits). The last letter "O" stands for op code, and its selection allows the user to change the contents of the memory location pointed to by the Program Counter. This location is referred to as op code since it is assumed that any location the Program Counter points to is to be executed and thus must contain a valid op code. After entering a selected letter the Monitor then responds with:

#### CHANGE TO ...

The maximum number of HEX digits that can be entered depends on which of the letters is chosen. The value entered will then replace the current contents and the registers are redisplayed.

"D" The Dump command allows the user to view the memory contents of any given section of memory. The contents are displayed in HEX with the associated ASCII characters displayed as well.

When the Dump command is issued the Monitor responds with:

#### STARTING ADDRESS..

The user then enters the starting address (up to 4 HEX digits are valid) of the section of memory to be Dumped.

After entering the starting address the Monitor then asks:

#### NUMBER OF BYTES..

The user then enters the number of bytes to display on the screen. Up to 3 HEX digits are valid and this number, as with most numbers returned by EMOS, is a HEX value. The Dump command automatically rounds this value so as to display a full line of 16 bytes.

The Edit commands allows the user to easily enter and modify code or data in successive memory locations.

When the Edit command is issued the Monitor responds with:

#### STARTING ADDRESS..

"E"

The user then enters the starting address of where code is to be entered or modified. Up to 4 HEX digits are valid. The Edit command will then display this address and its contents. The user then enters the new contents (up to 2 HEX digits). The next successive address is then displayed with its contents. If the user does not want to change the contents of this address, he simply presses the <ENTER> key and the next successive address and memory contents are displayed. The ability to "backtrack " is also available; typing a minus sign " - " followed by one Hex digit (1 - F) will decrement the address pointer by the amount of the digit. To quit editing and return to the monitor prompt, press the <ESC> key.

"F" The Fill command allows the user to Fill the memory contents of any given section of memory with a given byte.

When the Fill command is issued the Monitor responds with:

#### STARTING ADDRESS..

The user then enters the starting address of the section of memory to be Filled. Up to 4 HEX digits are valid.

The Monitor then requests:

#### NUMBER OF BYTES..

The user then enters the number of memory bytes to Fill. Up to 3 HEX digits are valid.

The Monitor then requests:

#### FILL BYTE..

The user enters the byte (up to 2 HEX digits) to fill the selected memory with.

"G" The Go command allows the user to execute a program in memory at full speed with an optional breakpoint. The program will continue to execute until the breakpoint is encountered, a key is pressed, or until a RST 7 (FFH) instruction is executed.

When the Go command is issued the Monitor responds with:

#### STARTING ADDRESS..

The user then enters the starting address of the program to be executed. Up to 4 HEX digits are valid. If only the <ENTER> key is pressed the program will start to execute from the current contents of the Program Counter.

The Monitor then requests:

#### **BREAKPOINT ADDRESS..**

The user then enters the address (up to 4 HEX digits) of where the user wishes the execution to stop.

**Note:** If the program execution never reaches the breakpoint address or the breakpoint address is not that of an op code the program will not stop at the breakpoint address. If the <ENTER> key is pressed without entering the breakpoint address, no breakpoint is set.

"H" The Hex/Dec math command provides the user with the sum and difference of two numbers. This command allows the user to declare the base of the numbers that will be entered as either Hexadecimal or Decimal.

When the Hex/Dec command is issued, the monitor responds with:

#### DEC OR HEX (D/H)...

After a D (for Decimal) or an H (for Hexadecimal) is entered, the monitor responds with:

#### **1ST NUMBER...**

Enter the number, up to 4 digits for HEX or 5 digits for DEC, in the chosen base. The monitor then responds with:

#### 2ND NUMBER...

Enter the second number, up to 4 digits for HEX or 5 digits for DEC, in the chosen base. The monitor will respond with:

| HEX SUM  | = xxxx DEC SUM  | = xxxx | SIGNED DEC SUM  | = xxxx |

|----------|-----------------|--------|-----------------|--------|

| HEX DIFF | = xxxx DEC DIFF | = xxxx | SIGNED DEC DIFF | = xxxx |

where xxxx is the result of the math operation. **NOTE:** To convert a number from one base to another, choose 0 as the response to the second number prompt.

"I" The Input command allows the user to Input the contents of an I/O port. The I/O address is an 8 bit HEX value and the content is also an 8 bit value displayed in HEX.

When the Input command is issued the Monitor responds with:

#### I/O PORT ADDRESS..

The user then enters the I/O address of the port to be read from. Up to 2 HEX digits are valid.

After entering the I/O port address the Monitor will respond with:

#### CONTENTS OF THE I/O PORT IS .. xx

where xx represents the contents of the specified I/O port displayed as an 8 bit hex value.

"L" The List command allows the user to view 16 machine language instructions beginning at any address in memory. The information that will be displayed, is the memory address of the instruction, its op code and then the mnemonic. All numbers displayed are in hex.

When the List command is issued the Monitor responds with:

#### STARTING ADDRESS..

The user then enters the starting address (up to 4 HEX digits are valid) of the section of memory to be Listed.

The 16 machine language instructions will be listed followed by the message...

#### ESC TO QUIT, ANY KEY TO CONTINUE.

If ESC is pressed the command will be aborted. If any other key is pressed, another 16 lines of instructions will be listed.

"M" The Move command allows the user to Move the memory contents of any given section of memory to another memory location. The source memory contents are left intact.

When the Move command is issued the Monitor responds with:

#### SOURCE ADDRESS..

The user then enters the source address of the section of memory to be moved. Up to 4 HEX digits are valid. After entering the starting address the Monitor then asks:

#### **DESTINATION ADDRESS..**

The user then enters the destination address of the section of memory to Move the source contents to. After entering the destination address (up to 4 HEX digits) the Monitor then prompts for the:

### NO. OF BYTES..

The user then enters the number of memory bytes to Move. Up to 3 HEX digits are valid and this number is a HEX value.

"O" The Output command allows the user to output an 8 bit HEX value to a specified I/O port address. The I/O port address is entered as an 8 bit HEX value.

When the Output command is issued the Monitor responds with:

#### I/O PORT ADDRESS..

The user then enters the I/O address of the port to be written to. Up to 2 HEX digits are valid.

The Monitor will respond with:

#### I/O DATA BYTE..

The user then enters the 8 bit HEX value to be written to the specified I/O port address.

"P" This will allow you to choose to write to the parallel printer port all subsequent characters that are displayed on the terminal.

When the Printer command is issued the Monitor responds with:

#### TURN PRINTER ON? (Y/N)..

If the user types "Y" then the above monitor response and all characters that are displayed to the terminal will also be written to the parallel printer port, otherwise if any other character is typed, characters will only be displayed on the terminal.

- "R" The Register command displays the current contents of all accessible CPU registers, the flags, the value on the top of the stack and the op code pointed to by the Program Counter and the mnemonic of that op code.

- **"S"** The MOS Service call allows the user to access EMOS Services without having to execute a CALL instruction.

When the Service command is issued, the monitor prompts the user for:

#### SERVICE NUMBER ..

For a listing of the available service calls, consult the section on EMOS services in this manual.

**NOTE:** The input parameters must be placed in the appropriate registers, before executing the S command. The C register is automatically loaded with the service number.

**"T"** The Trace command executes a single instruction and displays the register contents after each instruction.

**Note:** Since the Trace command is performed through software, operand fetches are not shown.

When the Trace command is issued the Monitor prompts the user for:

#### NUMBER OF INSTRUCTIONS..

The user enters up to a 2 HEX digit, value. This value determines the number of instructions executed. After each executed instruction the register contents are displayed. If the user does not enter the number of steps, but hits the <ENTER> key, then 1 instruction is executed.

**NOTE:** Instructions in EPROM cannot be traced so if a service call is traced, the service call is executed at full speed and, upon returning to the calling program, the Trace command resumes execution.

"W" The Write command allows the user to write the contents of memory to a RAMDISK block (or blocks).

When the Write command is issued the Monitor responds with:

## SOURCE ADDRESS ...

Enter the starting memory address (up to 4 HEX digits) of the data to be copied.

The Monitor then responds with:

#### **STARTING BLOCK ...**

Enter the block in RAMDISK (up to 3 DEC digits) where the data is to be stored.

The Monitor then responds with:

### NUMBER OF BLOCKS ...

Enter the number of blocks (up to 3 DEC digits) that will be needed to store the data.

If (STARTING BLOCK + NUMBER OF BLOCKS) is greater than 255 the error message

#### ERROR BLOCK OUT OF RANGE!

will be displayed, no Write action will be done, and the original prompt will return. **REMEMBER:** The size of a block is 256 bytes.

">" The Hex upload command loads data from the host to the trainer in Intel HEX format.

When the upload command is issued, the Monitor responds with:

#### STARTING ADDRESS ...

This is the memory address in the trainer where the data is to be loaded (up to 4 HEX digits.) The Monitor responds with:

## READY TO RECEIVE, <ESC> TO ABORT

The transfer of data can be stopped by pressing <ESC>.

"<" The Hex Download command saves data from the trainer to the host in Intel HEX format.

When the Download command is issued, the Monitor responds with:

## STARTING ADDRESS ...

This is the starting memory address (in the trainer) of the data to be saved (up to 4 HEX digits).

The Monitor then responds with:

## LAST ADDRESS ....

This is the ending address of the data to be saved (up to 4 HEX digits).

The Monitor then responds with:

## **OFFSET ADDRESS ...**

The offset address is normally entered with the same address used for the starting address

prompt. To begin downloading, press the <SPACE> key. **NOTE:** This command is to be used in conjunction with a communication package running on a PC.

"?" The Help command displays the help menu which contains the Monitor commands and a short description of each command. This is the same menu that is shown when EMOS is first invoked.

### **MOS SERVICES**

The Monitor Operating System allows the user to access MOS services with a single function (subroutine) CALL to address 1000 Hex. In addition, all registers that are not used as input or output to the service are preserved. NOTE: Services that are underlined incorporate the COM1 and COM2 RS232 serial ports. In order to make use of these services a PC/Terminal device should be connected to the COM1 or COM2 serial connector. The services are as follows:

| SERVICE 0 | DEMO            | Demonstration; this service routine sends a pitch of increasing frequency to the speaker while flashing the output LEDs in conjunction with the pitch.                                                                                                                                                                        |

|-----------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | INPUT<br>OUTPUT | REGISTER C: 0<br>NONE                                                                                                                                                                                                                                                                                                         |

| SERVICE 1 | <u>CONIN</u>    | Console input; this service waits for a character from the communication port selected by register B. Note that the RST 5.5 interrupt is disabled until the service terminates.                                                                                                                                               |

|           | INPUT           | REGISTER C: 1                                                                                                                                                                                                                                                                                                                 |

|           | OUTPUT          | REGISTER B: Communication port number 1 or 2.<br>REGISTER L: ASCII character returned from keyboard.                                                                                                                                                                                                                          |

| SERVICE 2 | <u>CONSTAT</u>  | Console input status; this examines the communication port selected by register B and returns a 0FFH if a character is ready, otherwise a 00H.                                                                                                                                                                                |

|           | INPUT           | REGISTER C: 2<br>REGISTER B: Communication port number 1 or 2.                                                                                                                                                                                                                                                                |

|           | OUTPUT          | REGISTER L: Console status.                                                                                                                                                                                                                                                                                                   |

| SERVICE 3 | <u>CONOUT</u>   | Console output; this service outputs a ASCII character to the communication port selected by register B.                                                                                                                                                                                                                      |

|           | INPUT           | REGISTER C: 3<br>REGISTER B: Communication port number 1 or 2.                                                                                                                                                                                                                                                                |

|           | OUTPUT          | REGISTER E: ASCII character.<br>NONE                                                                                                                                                                                                                                                                                          |

| SERVICE 4 | <u>PSTRING</u>  | Print string; this service sends a string of characters to the communication port selected by register B. The string of ASCII characters starting at the address in the D/E register pair will be sent out until a "\$" is encountered. The "\$" is not printed and D/E is returned pointing to the character after the "\$". |

|           | INPUT           | REGISTER C: 4<br>REGISTER B: Communication port number 1 or 2.                                                                                                                                                                                                                                                                |

|           | OUTPUT          | REGISTER PAIR DE: Pointer to the start of the string.<br>REGISTER PAIR DE: This will point to the character after the "\$".                                                                                                                                                                                                   |

| SERVICE 5 | <u>UPRINT</u>   | Unsigned print; this service prints a 16 bit number in decimal,<br>without use of sign, to the communication port selected by<br>register B.                                                                                                                                                                                  |

|           | INPUT           | REGISTER C: 5<br>REGISTER B: Communication port number 1 or 2.                                                                                                                                                                                                                                                                |

|           | OUTPUT          | REGISTER PAIR DE: 16 bit unsigned number to print.<br>NONE                                                                                                                                                                                                                                                                    |

|           |                 |                                                                                                                                                                                                                                                                                                                               |

| SERVICE 6 | <u>SPRINT</u>   | Signed print; this service prints a 16 bit number in decimal with use of sign (2's complement), to the communication port selected by register B. |

|-----------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|           | INPUT           | REGISTER C: 6<br>REGISTER B: Communication port number 1 or 2.                                                                                    |

|           | OUTPUT          | REGISTER PAIR DE: 16 bit signed number to print.<br>NONE                                                                                          |

| SERVICE 7 | MULT            | Multiply; this service multiplies HL by DE and returns the result in HL and                                                                       |

|           | INPUT           | DE.<br>REGISTER C: 7<br>REGISTER PAIR DE: 16 bit multiplier                                                                                       |

|           | OUTPUT          | REGISTER PAIR HL: 16 bit multiplicand<br>REGISTER PAIR HL: Upper 16 bits of product.<br>REGISTER PAIR DE: Lower 16 bits of product                |

| SERVICE 8 |                 | Divide; this service divides HL by DE.                                                                                                            |

|           | INPUT           | REGISTER C: 8<br>REGISTER PAIR HL: 16 bit dividend.                                                                                               |

|           | OUTPUT          | REGISTER PAIR DE: 16 bit divisor.<br>REGISTER PAIR HL: 16 bit quotient.                                                                           |

|           |                 | REGISTER PAIR DE: 16 bit remainder.                                                                                                               |

| SERVICE 9 | ADCIN           | Analog to Digital input; this service reads a 8 bit value from a selected A/D channel.                                                            |

|           | INPUT           | REGISTER C: 9<br>REGISTER E: Selected channel number 0, 1, 2 or 3.                                                                                |

|           | OUTPUT          | REGISTER L: 8 bit analog conversion.                                                                                                              |

| SERVICE A | DIPSWIN         | DIP switch input; this service reads the current switch positions of the 8 position DIP switch.                                                   |

|           | INPUT<br>OUTPUT | REGISTER C: A<br>REGISTER L: DIP switch value.                                                                                                    |

|           |                 |                                                                                                                                                   |

| SERVICE B | PTBIN           | Port B input; this service reads the contents of the digital input port B and returns its complement in L. This is similar to service A.          |

|           | INPUT<br>OUTPUT | REGISTER C: B<br>REGISTER L: Complement of 8 bit port B value.                                                                                    |

| SERVICE C | PTAOUT          | Port A output; this service writes to the digital output port A.                                                                                  |

|           | INPUT           | REGISTER C: C<br>REGISTER E: 8 bit value to write to port A (this port is equipped with 8                                                         |

|           | OUTPUT          | status LED's).<br>NONE                                                                                                                            |

| SERVICE D | HEXPRINT        | Hex print; This service prints to the communication port selected by                                                                              |

|           | INPUT           | register B, the value in DE in base 16 (HEX). 4 HEX digits are printed.<br>REGISTER C: D                                                          |

|           |                 | REGISTER B: Communication port number 1 or 2.<br>REGISTER PAIR DE: 16 bit unsigned number to print.                                               |

|           | OUTPUT          | NONE                                                                                                                                              |

| SERVICE E       | DACOUT                 | Digital to Analog Converter output; This service routine outputs a 8 bit number in the E register to the Digital to Analog converter.                                                                                                                                      |

|-----------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | INPUT                  | REGISTER C: E<br>REGISTER E: 8 bit value to output to DAC.                                                                                                                                                                                                                 |

|                 | OUTPUT                 | NONE                                                                                                                                                                                                                                                                       |

| SERVICE 10      | РІТСН                  | Pitch output; This service sends the 16 bit count in the DE register pair to the speaker timer (8253 timer 1). The larger the number the lower the pitch. If the DE register pair = 0, then the speaker tone is turned off.                                                |

|                 | INPUT                  | REGISTER C: 10<br>REGISTER PAIR DE: 16 bit pitch value.                                                                                                                                                                                                                    |

|                 | OUTPUT                 | NONE                                                                                                                                                                                                                                                                       |

| SERVICE 11      | LEDOUT                 | LED Display output; This service routine displays a ASCII character in the E register to the LED alphanumeric display at the character position specified in the D register.                                                                                               |

|                 |                        | REGISTER C: 11<br>REGISTER E: ASCII character to display.<br>REGISTER D: Character position (positions are numbered 0 to 7 from left<br>to right).                                                                                                                         |

|                 | OUTPUT                 | NONE                                                                                                                                                                                                                                                                       |

| SERVICE 12      | LEDHEX                 | LED Hexadecimal output; This service routine displays a number<br>in the DE register pair in HEX, on the left 4 LED alphanumeric<br>displays.                                                                                                                              |

|                 | INPUT                  | REGISTER C: 12<br>REGISTER PAIR DE: 16 bit number to be displayed in HEX.                                                                                                                                                                                                  |

|                 | OUTPUT                 | NONE                                                                                                                                                                                                                                                                       |

| SERVICE 13      | LEDDEC                 | LED Decimal output; This service displays a number in the DE register<br>pair in decimal, left justified on the LED alphanumeric display (maximum<br>decimal value is 9999).                                                                                               |

|                 | INPUT                  | REGISTER C: 13<br>REGISTER PAIR DE: number to be displayed in Decimal.                                                                                                                                                                                                     |

|                 | OUTPUT                 | NONE                                                                                                                                                                                                                                                                       |

| SERVICE 14      | DELAY                  | Delay according to the value of the HL register pair. The larger the value, the longer the delay.                                                                                                                                                                          |

|                 | INPUT                  | REGISTER C: 14<br>REGISTER PAIR HL: The amount of delay.                                                                                                                                                                                                                   |

|                 | OUTPUT                 | NONE                                                                                                                                                                                                                                                                       |

| SERVICE 15 TUNE |                        | Play the tune which is in the string pointed to by DE at the tempo specified by B. The larger the value of B the longer the duration of each tone. If a zero is encountered in the string, then the subroutine terminates and returns DE pointing to the byte after the 0. |

|                 | INPUT                  | REGISTER C: 15<br>REGISTER B: Length of each tone.<br>REGISTER PAIR DE: Pointer to a string of tones.                                                                                                                                                                      |

| the string.     | OUTPUT                 | REGISTER PAIR DE: This is returned pointing to the byte after the 0 in                                                                                                                                                                                                     |

| SERVICE 16      | <b>PRNOUT</b><br>INPUT | Send the character in E to the parallel printer port.<br>REGISTER C: 16                                                                                                                                                                                                    |

|                 | OUTPUT                 | REGISTER E: Character to be sent to the printer.<br>REGISTER L: This will be 0 if no errors occured. If an error occured then<br>the bits in L will be returned indicating the following:                                                                                  |

|            |                                 | Bit 3 = Indicates a printer error in general, if it is 1.<br>Bit 4 = Means printer not selected, if 0.<br>Bit 5 = Indicates printer out of paper, if 1.<br>Bit 7 = Printer is busy, if 0.                                                             |

|------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SERVICE 17 | OUT422<br>INPUT                 | Send the byte in E out the RS422 port.<br>REGISTER C: 17<br>REGISTER E: Character to output                                                                                                                                                           |

|            | OUTPUT                          | NONE                                                                                                                                                                                                                                                  |

| SERVICE 18 | <b>IN422</b><br>INPUT<br>OUTPUT | Get a byte from the RS422 port.<br>REGISTER C: 18<br>REGISTER PAIR HL: If a character has been received, H will be 1 and L<br>will be the character. HL will be 0 if a character has not been received.                                               |

| SERVICE 19 | KEYIN                           | Wait for a byte from the keypad and return it in L. Reading the keys starting at the top row and reading from left to right as you go down, the values returned for the first 16 keys will be 00 to 0F hex. The next 3 rows will return 14 to 1F hex. |

|            |                                 | REGISTER C: 19                                                                                                                                                                                                                                        |

|            | OUTPUT                          | REGISTER L: Numeric value of key pressed                                                                                                                                                                                                              |

| SERVICE 1A | WRSCL                           | Write 8 bytes of memory, starting from the address in DE, to the optional real time clock. The clock provides timekeeping                                                                                                                             |

**TA WRSCL** Write 8 bytes of memory, starting from the address in DE, to the optional real time clock. The clock provides timekeeping information in BCD including hundredths of seconds, seconds, minutes, hours, day, date, month and year information. The date at the end of the month is automatically adjusted for months with less than 31 days, including correction for leap years. The real time clock operates in either 24-hour or 12-hour format with an AM/PM indicator. The data pointed to by DE will be stored in the real time clock as follows:

|        | BIT 7 BIT                                                                            | 0 RANGE       |       |

|--------|--------------------------------------------------------------------------------------|---------------|-------|

| DE     | 0.1 SEC   0.01 SEC                                                                   | ו<br>ן        | 00-99 |

| DE + 1 | 0   10 SEC   SECONDS                                                                 | ו<br>ן        | 00-59 |

| DE + 2 | 0   10 MIN   MINUTES                                                                 | 1<br>]        | 00-59 |

| DE + 3 | (AM/PM mode)<br>1   0  AM/PM 10 HR  HOURS<br>(24 hour mode)<br>0   0   10 HOUR HOURS | 1  <br>J<br>J | 01-12 |

| DE + 4 | 0   0  STOP   0   DAY                                                                |               | 01-07 |

| DE + 5 |                                                                                      | '<br> <br>]   | 01-31 |

| DE + 6 | 0      | 0  |      | 10MTH | MONTH | 01-12 |

|--------|--------|----|------|-------|-------|-------|

| DE + 7 | гт<br> | 10 | YEAR |       | YEAR  | 00-99 |

If bit 7 of address DE + 3 is 0 the clock will be in 24 hour mode after WRSCLK is executed. If it is 1 then AM/PM mode is selected and bit 5 of address DE + 3 will select AM or PM (PM is selected if bit 5 is 1). When changing from AM/PM mode to 24 hour mode and vice-versa you must change the hours to match the selected mode. Once the hours are correct, the real time clock will maintain the correct hour for the selected mode. If bit 5 of address DE + 4 is set to 1 and WRSCL is executed, the real time clock will

be stopped. The clock may be restarted by resetting the bit to 0 and executing WRSCL.

INPUT REGISTER C: 18 REGISTER PAIR DE: Address of the first of 8 bytes to be written to the real time clock. OUTPUT NONE

| SERVICE 1B | RDSCL  | Read 8 bytes of data from the optional real time clock and store them in the 8 consecutive bytes starting at the address in the DE register pair. The 8 bytes are formatted the same as the data passed to WRSCL. |

|------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | INPUT  | REGISTER C: 19<br>REGISTER PAIR DE: Starting address to store the 8 bytes read from the real time                                                                                                                 |

| clock.     | OUTPUT | NONE                                                                                                                                                                                                              |

**EXAMPLE:** OUTPUT THE HEX NUMBER 1234 TO THE LED DISPLAY

| START: | MVI  | C,12H   | ; LEDHEX SERVICE ROUTINE                           |

|--------|------|---------|----------------------------------------------------|

|        | LXI  | D,1234H | ; LOAD REG PAIR D/E WITH HEX VALUE 1234            |

|        | CALL | 1000H   | ; CALL MOS FOR LEDHEX SERVICE                      |

|        | HLT  |         | ; HALT PROGRAM AND FREEZE DISPLAY. NORMALLY        |

|        |      |         | ; PROGRAMS TERMINATE WITH A RST 7 INSTRUCTION (FF) |

|        |      |         | ; WHICH WOULD OVERWRITE DISPLAY.                   |

## MACHINE LANGUAGE

| 8F01 | 0E | ; MVI  | C,12H   |

|------|----|--------|---------|

| 8F02 | 12 |        |         |

| 8503 | 11 | ; LXI  | D,1234H |

| 8F04 | 34 |        |         |

| 8F05 | 12 |        |         |

| 8F06 | CD | ; CALL | 1000H   |

| 8F07 | 00 |        |         |

| 8F08 | 10 |        |         |

| 8F09 | 76 | ; HLT  |         |

|      |    |        |         |

#### TERMINATING PROGRAMS

Each user program should end with the RST7 (FFH) software interrupt instruction. This instruction allows the Monitor Operating System to regain control of the CPU.

The Monitor Operating System also uses the RST7 instruction to implement a breakpoint when using the RUN key. If additional breakpoints are required they can be hand inserted at the appropriate spots in the user's program. It is the user's responsibility to remove these breakpoints when through.

## Software Single Stepping and Breakpoints

Single Stepping and Breakpoints make debugging software and hardware easier. Users can use these tools to determine if a program is functioning correctly and if not where the problem is located. Software Single Stepping and Breakpoints are most useful when the hardware is functioning properly and a program needs debugging. These software tools provide us with easier debugging and more information then their hardware counterparts. For example registers and memory contents may examined and changed, and addresses, data, and register contents are all displayed in HEX rather than binary. The hardware status LEDs display the contents of the address, data, and control busses all in binary. The Hardware Single Stepper and Breakpoints have couple advantages of their own. First, if the hardware is not working properly the hardware single stepper can be used to locate at what address the processor goes awry and what state the bus and address lines were in at that time. The hardware single stepper also can provide us with operand fetches as well as instruction fetches and memory accesses. Second, the hardware breakpoint can break at any address, even addresses in EPROM, and is not limited to instruction fetches as is the software breakpoint.

The Software Single Step is implemented as its name states through software. When the STP key is pressed, the instruction at the current PC address is executed. This is accomplished by the Monitor Operating System (MOS) replacing the byte prior to the instruction with an EI (FB hex) instruction. The MOS program then unmasks the RST 6.5 interrupt. This interrupt should be jumpered to VCC (JP3) so as to always produce an interrupt when the 6.5 interrupt is enabled and unmasked. The 8085 microprocessor always executes one instruction after the El instruction before enabling interrupts. That one instruction is the instruction that is to be single stepped. After the El instruction is inserted prior to the single step instruction, the MOS program jumps to the EI instruction. After the EI instruction executes, the single step instruction is executed before the RST 6.5 interrupt is acknowledged. When the RST 6.5 interrupt is acknowledged the execution branches back to the MOS program. The MOS program then replaces the byte back at its original address overwriting the EI instruction. The current user PC address is found by POPing the return address from the interrupt off the stack. Since software single stepping requires the byte prior to the instruction to be replaced with an El instruction, software single stepping can only take place in RAM. When software single stepping into a MOS Service CALL, which are located in EPROM, the processor will execute the service CALL full speed and break at the instruction immediately following the service CALL. Software single stepping, steps an instruction at a time, so no operand fetches or memory writes are seen.

The Software Break allows the user to run a program full speed and break (stop) the program at a user specified address. The address is entered from the keypad in conjunction with SFT BRK key. The software break is performed by the MOS program using the RST 7 software interrupt. When the user specifies a break address the Monitor Operating System replaces the opcode at this address with RST 7 (FF hex) instruction. The users program can then execute full speed until encountering the RST 7 instruction. When the users program reaches the break, the RST 7 instruction returns control to the MOS program only allows the use of one breakpoint, which is automatically reset to 0000 after the breakpoint has been encountered. The users program. Remember that any hand inserted breakpoints must also cleared by hand. When inserting a software breakpoint it is important to remember that if the program execution never reaches the breakpoint address is not that of an opcode, the program will not stop at the breakpoint address below 8000 HEX) will not stop execution, even if the opcode at that address is executed.

## Hardware Single Stepping and Breakpoints

To facilitate software/hardware inspection and trouble shooting, the trainer has a hardware single step system built in. Upon trainer power up, the Single Step circuit is disabled, and the CPU runs full speed. Should an application program need debugging, the single step system can be enabled by the HSS EN button, on PB2. The single step circuit gives a choice of stopping on all READS and all WRITES, pushbutton ALL R/W or stopping on INSTRUCTION FETCHES only, pushbutton INS FET. The ALL R/W button causes the single stepper to step at all fetches and memory writes while the INS FET button only step on instruction fetches much like the software single step. The POWER ON RESET and the CPU RESET are separate, so the CPU may be reset, without disturbing the single stepper, where the processor is always executing MOS or user instructions, the hardware single stepper utilizes wait states in order to single step the processor. Thus the microprocessor is not executing any instructions (is idle) between hardware steps. The Single Stepper can be turned on or off at any time through the use of the HSS EN key. Note: the user should be aware if the single step enable LED is lit (hardware single stepper is enabled), as this will prevent the processor from executing.

The Hardware Breakpoint on the Universal Trainer is comprised of two 8 bit latches and an arming circuit. The Monitor Operating System loads these latches and arms the arming circuit when the HRD BRK and ENT keys are pressed. The address entered from the keypad is split and sent to the high (01 hex) and low (00 hex) address latches, after which the arming circuit (02 hex) is armed. When armed, as the trainer CPU accesses each address, whether it is an instruction or data, the addresses are compared to the latched address. When a match occurs, the comparator instantly engages (turns on) the hardware single stepper system. Simultaneously, the comparator disarms itself. With the hardware single stepper now ON, the CPU is stopped at this address, and the code can now be examined step by step by pushing the HSS button. Full speed execution can be continued by disabling the hardware single stepper. After a hardware breakpoint occurs the arming circuit is automatically disarmed. MOS however still keeps the break address in memory until another breakpoint is set or the system is reset. To rearm the previous breakpoint simply press the HRD BRK key followed by the ENT key. Note: if a hardware breakpoint is set and armed, examining memory using the ENT key or the DEC key will stop the processor if the breakpoint address is examined.

## The TRAP key

A program that is running without breakpoints can be terminated by pressing the TRAP key. When the key is pressed, either MOS or EMOS (depending on which monitor started the program) will regain control, allowing you to examine the values of the registers and set software or hardware breakpoints.

## USING INTERRUPTS

The Universal Trainer has 13 interrupts available to the user. Five are standard on the 8085A CPU and eight are available through the 8259a Multi-level interrupt controller chip. When utilizing interrupts the Single Step feature of the Monitor System may not function correctly. It is recommended when using interrupts to run at full speed for predictable results.

The 8085A CPU has five (5) on-chip hardware restart/interrupts. These are general purpose interrupts found on all 8085 CPU chips. This listing includes the trainer subsystems to which each interrupt is wired.

## 1. TRAP ------ PUSHBUTTON

The TRAP interrupt is a non-maskable interrupt and is the highest priority interrupt. It is positive edge and level sensitive. The trainer system provides a pushbutton on keypad PB1 which allows a program running at full speed to be stopped and control given back to MOS or EMOS without resetting the trainer.

2. RST7.5 ------ PUSHBUTTON or TIMER #2

The RST7.5 interrupt is a latched positive edge sensitive restart interrupt. A low to high transition at RST7.5 input (pin 7) sets a flip-flop. An interrupt can be generated by the output of timer #2 or by pressing the INT 7.5 pushbutton.

- 3. RST6.5 ----- EXPANSION/Vcc

- 4. RST5.5 ----- KEYPAD

The RST6.5 and RST5.5 interrupts are level sensitive only. They respond to the interrupt pin (8 for RST6.5, 9 for RST5.5) when the pin is logic high. The pin must be held high until the CPU can get around to servicing the interrupt or it will be missed. Although the RST6.5 can be jumpered to the Expansion connector, it is normally left tied to +5V via jumper JP3, because MOS uses it for software single stepping. RST5.5 is reserved for use by the LED/KEYPAD controller, and has no jumper options.

The RST interrupts will vector to EPROM and from there they are vectored again to RAM by the MOS. The RAM vectors for RST5.5, RST 6.5 and RST7.5 start at memory addresses FFE5, FFE7 and FFE9 respectively. For example, to vector the RST 5.5 interrupt to a service routine at 90F3h, store the low byte of the address (F3h) at FFE5 and the high byte (90h) at FFE6. Remember that MOS uses RST6.5 for software single stepping, so do not change the data at FFE7 or FFE8 if you want to use single stepping.

The RST7.5, RST6.5, and RST5.5 interrupts are software maskable, which means they can be enabled/disabled by software, independently or in unison.

## 5. INTERRUPT (general 8080 interrupt) --- CONTROLLER

The remaining interrupt pin is the true interrupt system input pin, and it works the same as in the 8080 CPU system, which the 8085A is the offspring of. This interrupt can also be enabled and disabled by software. When a high is seen on the INTR (pin 10 of the CPU), the CPU issues an interrupt acknowledge, signal INTA\*, which signals the interrupting device to place an interrupt vector address on the Data bus. In the EMAC trainer, this is accomplished with the use of the 8259A Multi-level interrupt controller chip. It has eight (8) interrupt request inputs, and upon receipt of an interrupt request, it generates an INTR to the CPU, and handles all INTA\* handshaking cycles. The user must program the 8259A to accept level or edge sensitive active high interrupt requests, to resolve interrupt priority, end of interrupt type, and the interrupt vectors passed for each interrupt.

The 8259 Interrupt Controller pin assignments are as follows :

- 6. IRQ0 Expansion Connector ext. interrupt or Pushbutton

- 7. IRQ1 Communication port 1 Receive Ready

- 8. IRQ2 Com. port 1 Transmit Ready

- 9. IRQ3 Com. port 2 Receive Ready

- 10. IRQ4 Com. port 2 Transmit Ready

- 11. IRQ5 Timer 0 (prescaler)

- 12. IRQ6 Timer 2

- 13. IRQ7 A/D Conversion Complete

The trainer provides pushbuttons (PB1) to allow manual triggering of various interrupts. PB1 is a four station keypad switch, that is connected to CPU RESET, interrupt RST7.5, TRAP, and interrupt controller IRQ0. All pushbutton interrupts are debounced with an R-C network and Schmitt Trigger invertor gate. IRQ0 is shared with the expansion connector input INT0. Jumper JP25 inhibits the external input to allow the pushbutton interrupt to function independently.

## HARDWARE REFERENCE

## EMAC TRAINER BOARD AND CIRCUIT DESCRIPTIONS

The EMAC UNIVERSAL TRAINER is an 8085 based CPU system, utilizing the INTEL 8085A microprocessor. The trainer is a fully functional industrial control board, but with certain embellishments to allow the student to easily probe the inner workings of an operational microprocessor system.

The board has been laid out to provide easy access to the DATA, ADDRESS, and CONTROL busses. The trainer features analog as well as digital I/O, and it also has many connectors to permit installation of user constructed prototype and expansion cards.

The trainer incorporates many jumpers to select options such as memory configuration, communication baud rates, etc. and also to provide simulated hardware faults. The instructor can set these fault programming jumpers to create circuit " failures " the user must find in order to hone his trouble shooting skills.

The trainer has many subsystems on it that allow the user to "get his feet wet" on many types of circuit design methods. Among them are :

- 1. Switching power supplies

- 2. Linear power supply regulators

- 3. Local/expansion data busses

- 4. Memory Mapped I/O and I/O mapped I/O

- 5. Analog and Digital I/O.

- 6. Multi-sourced interrupts.

The trainer has a number of Input/Output devices on it as well. Among them are:

- 1. 2 RS-232 serial ports, one of which is optional on the military version

- 2. 1 RS-422/485 serial port

- 3. Keypad and alphanumeric LED display

- 4. 4 channel, 8 bit analog to digital converter

- 5. 1 Parallel printer port

- 6. 3 channel Timer/Counter ( with speaker on one channel )

- 7. Digital I/O with status LED's

- 8. 8 level Interrupt Controller